UDT E1 T1 Clocks

Clock Controllers are built in LD 73, and enabled in LD 60. On Rls 5.0 and above the clocking is a little bit different. Each Media Gateway with a digital service must have a clock controller in it. If the main clock is tied to an E1 then all clocks must be E1 clocks.

Typical Rls 5.0 and above hardware:

- NTDW79 - E1/T1 Universal Digital Trunk (UDT) card;

- NTDW12 - Clock Controller daughter board.

To identify which media gateway slot contains which PRI loop, print CEQU in LD 22.

To identify which PRI card has a clock controller daughter board, print PRI2, SYTI in LD 73.

Clock Configuration:

Place the UDT/PRI/DTI card (with Clock Controller) close to the MGC, preferably in slot one.

Remember, UDT cards must be configured via a TTY first, depending on the circuit configuration.

Define clock controller parameters in LD 73, data is always CHanGed:

REQ chg TYPE pri2 Either PRI2/DTI2/JDMI/DDB FOR T1 FEAT syti MGCLK 0 0 1 <loop> <shelf> <card> of UDT pack with a clock daughter board PREF 1 Card-slot of the loop providing the Primary Reference (= MGCLK card) SREF Secondary reference (if applicable), or <enter> MGCLK Enter next MG, or <enter> to finish

Note: To remove a configured Clock Controller use CHG, but at MGCLK precede <loop> <shelf> with "X". For example:

REQ chg TYPE pri2 FEAT syti MGCLK x0 0 x to remove CC in <loop> <shelf>, a "card" parameter is not required

Loop and shelf parameters reference the Media Gateway Superloop with the UDT pack, not the PRI loop number.

Each Media Gateway (with digital services) requires a clock controller. Print SYTI (or DDB) in LD 73 to list them.

Clock Maintenance:

A clock controller can operate in one of two modes: tracking and non-tracking (free-run).

Tracking: The clock controller will try and lock to a reference PRI's clock (PREF or SREF, LD 73). If the clock reference is stable, the clock controller will "track" it. There are two stages to clock controller tracking: tracking a reference, and locked onto a reference. The clock controllers should be locked to the reference clock. The secondary reference acts as a backup to the primary reference.

Free-run (non-tracking): The clock controller does not refence any source, but provides its own clock to the system, eg, a Master. Free-run is undesirable if the system is intended to be a slave. If both PREF and SREF are lost, the system will revert to Free-run.

Clock controller commands in LD 60:

enl cc l s(where l=superloop; s=shelf)

Enable the specified clock controller (loop and shelf).dis cc l s(where l=superloop; s=shelf)

Disable the specified clock controller (loop and shelf).ssck l s(where l=superloop; s=shelf)

Check status of the specified clock controller (loop and shelf).trck aaa l s(Where aaa = PCK, SCLK, or FRUN; l=superloop; s=shelf)

Track MG shelf to the primary or secondary clock reference, or enable free-run (master) mode.

ALWAYS disable the Loop, DCH, MSDL, and CC daughterboard (if fitted) before unseating/replacing a UDT card. Failure to do so will cause the MGC to reboot!

ALWAYS disable the Loop, DCH, MSDL, and CC daughterboard (if fitted) before unseating/replacing a UDT card. Failure to do so will cause the MGC to reboot!Clock Status:

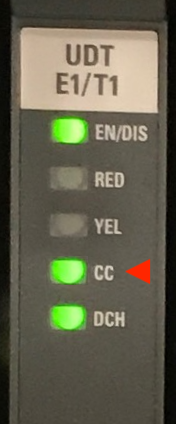

The front panel CC LED displays clock status, if the LED is off, a Clock Controller daughterboard is not equipped.

- CC LED:

- Unequipped

- Disabled

- Enabled and locked (or free-run)

- Tracking mode (synchronisation)

A clock controller may track it's primary clock (PCK), or secondary clock (SCLK) reference, or set to free run (FRUN) mode.

If you experience excessive slips after a PRI outage (DTA103 errors), its very likely that the clock controller is either disabled, or has switched to free-run, when it should be tracking/locked. Its good practice to check the clock status after a circuit returns to service.

To find UDT CC daughter board location(s), go to LD 73 and print PRI2 SYTI (system timers):

>LD 73

REQ: PRT

TYPE: PRI2

FEAT: SYTI

MGCLK 0 0 1 Superloop, shelf, and card number of Clock Controller for IPMG

PREF 0 0 1 Primary clock Reference PRI card, usually the PRI on this card

SREF 0 0 2 Secondary clock Reference PRI card, cannot be the same as PREF

MGCLK 4 0 1

PREF 4 0 1

SREF (specifying an SREF is optional)

CCGD 15 Clock Controller free run Guard time

CCAR 15 Clock Controller Audit Rate

To check the status of UDT CC daughter board(s), go to LD 60 and enter SSCK:

>LD 60

.ssck 0 0

ENBL Use enl cc l s to enable the clock controller if necessary

CLOCK ACTIVE

CLOCK CONTROLLER - LOCKED TO SLOT 1

PREF - 1

SREF - 2

AUTO SWREF CLK - ENBL

.ssck 4 0

ENBL

CLOCK ACTIVE

CLOCK CONTROLLER - FREE RUN

PREF - 1

SREF -

AUTO SWREF CLK - ENBL

Clock Tracking:

To force a clock controller to track to the primary clock source (often the PRI on the same card):

.enl cc 0 0 Enable clock controller in MG <loop> <shelf>: 0 0 .trck pck 0 0 Set clock controller tracking for MG <loop> <shelf>: 0 0 .ssck 0 0 Check clock is enabled, active, locked to PREF card

Reset the loop alarm counters with RCNT <pri_loop> after changing the tracking mode.

STAT the PRI in LD 60 to confirm it has an enabled and tracking clock reference:

PRI2 LOOP 201 - ENBL REF CLK: ENBL clock is enabled TRACKING clock is tracking on this loop SERVICE RESTORE: YES ALARM STATUS ACCEPTABLE. :

Instead of:

PRI2 LOOP 201 - ENBL REF CLK: DSBL * the clock must be enabled to prevent slips! SERVICE RESTORE: YES ALARM STATUS ACCEPTABLE. :

* If REF CLK shows DSBL, enter ENL CC <loop> <shelf> again, even if SSCK shows it ACTIVE, and STAT again.

DTI0061 messages indicate the circuit is not tracking the primary clock reference.

Enter: ENL CC <loop> <shelf> and TRCK PCK <loop> <shelf> to correct it.

Remember to RCNT <pri_loop> to reset the loop counters after excessive slips.

Note that establishing "tracking" can take several minutes, and during synchronisation, the cards CC LED will flash green.

Also refer to: UDT E1/T1 - Universal Digital Trunk card